进阶篇 V [Clock Tree]

项目&教程仓库:-STM32-RoboMaster-

1.0 什么是Clock Tree?

1.1 定义

时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。时钟系统就是CPU的心脏,决定CPU速率,像人的心跳一样 只有有了心跳,人才能做其他的事情,而单片机有了时钟,才能够运行执行指令,才能够做其他的处理(点灯,串口,ADC),时钟的重要性不言而喻。

STM32本身十分复杂,外设非常多 但我们实际使用的时候只会用到有限的几个外设,使用任何外设都需要时钟才能启动,但并不是所有的外设都需要系统时钟那么高的频率,为了兼容不同速度的设备,有些高速,有些低速,如果都用高速时钟,势必造成浪费 并且,同一个电路,时钟越快功耗越快,同时抗电磁干扰能力也就越弱,所以较为复杂的MCU都是采用多时钟源的方法来解决这些问题。所以便有了STM32的时钟系统和时钟树。

- STM32时钟系统主要的目的就是给相对独立的外设模块提供时钟,也是为了降低整个芯片的耗能。

- 系统时钟,是处理器运行时间基准(每一条机器指令一个时钟周期)

- 时钟是单片机运行的基础,时钟信号推动单片机内各个部分执行相应的指令。

- 一个单片机内提供多个不同的系统时钟,可以适应更多的应用场合。

- 不同的功能模块会有不同的时钟上限,因此提供不同的时钟,也能在一个单片机内放置更多的功能模块。

- 对不同模块的时钟增加开启和关闭功能,可以降低单片机的功耗

- STM32为了低功耗,他将所有的外设时钟都设置为disable(不使能),用到什么外设,只要打开对应外设的时钟就可以,其他的没用到的可以还是disable(不使能),这样耗能就会减少。这就是为什么不管你配置什么功能都需要先打开对应的时钟的原因。

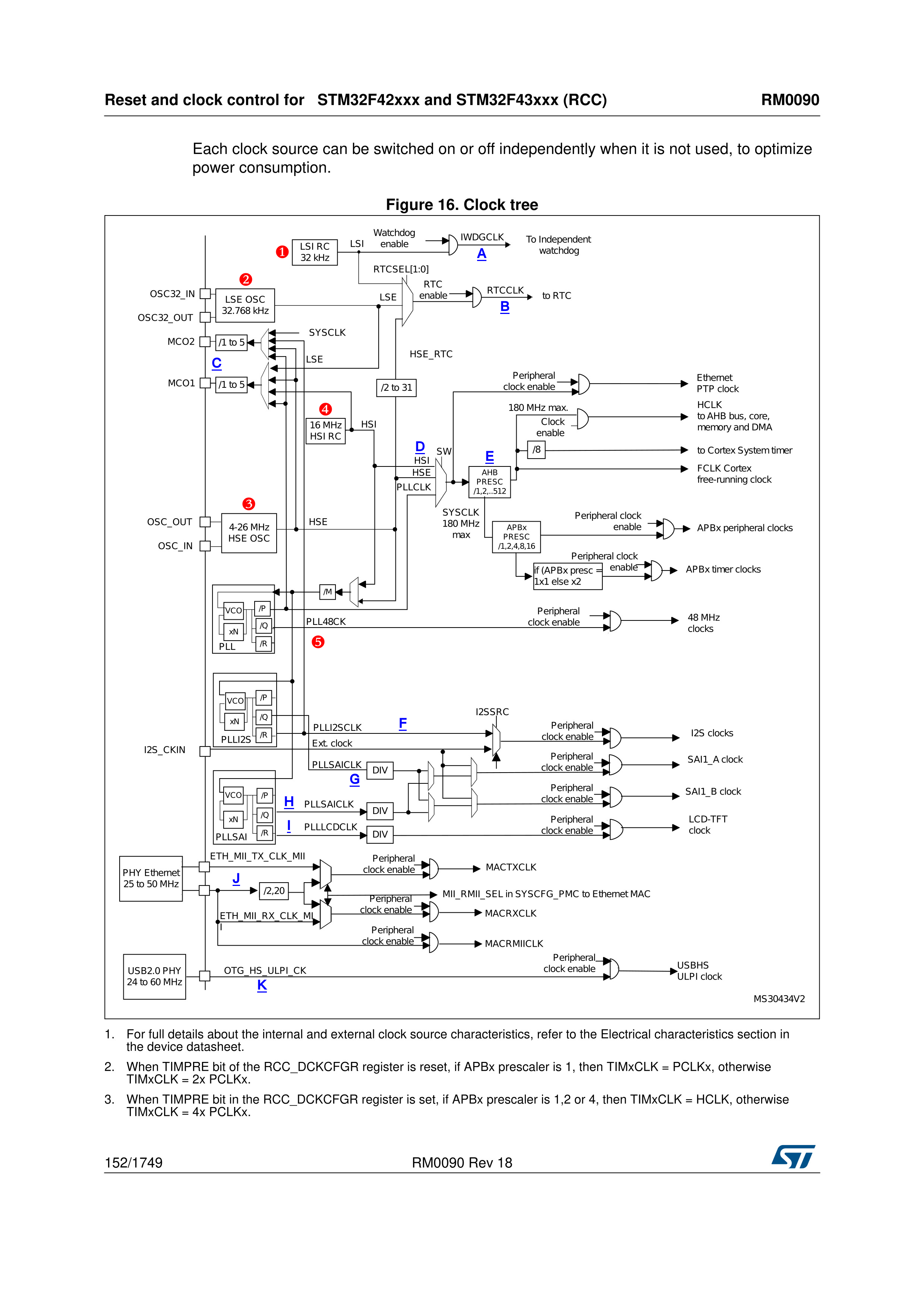

1.2 解析

先不要被吓到,我们慢慢来一条线一条线地梳理清楚。

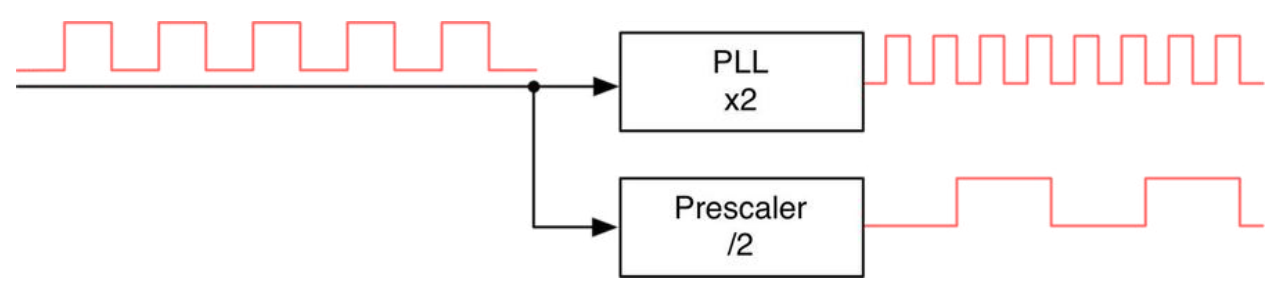

除了时钟,有两个概念必须提前讲解

- Phase-Locked Loop ( PLL ) :锁相环 的作用是整数倍地增高频率

- Prescaler:预分频器 的作用是整数倍地降低频率

在STM32F4系列中,有5个最重要的时钟源,为HSI、HSE、LSI、LSE、PLL。其中PLL实际是分为三个时钟源,分别为主PLL和I2S部分专用PLLI2S和SAI部分专用PLLSAI。从时钟频率来分可以分为高速时钟源和低速时钟源,在这5个中HSI,HSE以及PLL是高速时钟,LSI和LSE是低速时钟。从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的方式获取时钟源,其中HSE和LSE是外部时钟源,其他的是内部时钟源。

- ❶ LSI:Low Speed Internal 低速内部时钟,RC振荡器,频率为32kHz左右,供独立看门狗和自动唤醒单元使用

- ❷ LSE:Low Speed External 低速外部时钟,接频率为32.768kHz的石英晶体,这个主要是RTC的时钟源

- ❸ HSE:High Speed External 高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~26MHz,HSE也可以直接做为系统时钟或者PLL输入

- ❹ HSI:High Speed Internal 高速内部时钟,RC振荡器,频率为16MHz,可以直接作为系统时钟或者用作PLL输入

- ❺ PLL:Phase-Locked Loop 锁相环倍频输出,STM32F4有三个PLL

- 主PLL由HSE或者HSI提供时钟信号,并具有两个不同的输出时钟,第一个输出PLLP用于生成高速的系统时钟(最高180MHz);第二个输出PLLQ为48M时钟,用于USB OTG FS时钟,随机数发生器的时钟,和SDIO时钟

- 第一个专用PLL ( PLLI2S ) 用于生成精确时钟,在I2S和SAI1上实现高品质音频性能,其中,N是用于PLLI2S vco的倍频系数,其取值范围是:192~432;R是I2S时钟的分频系数,其取值范围是:2~7;Q是SAI时钟分频系数,其取值范围是:2~15;P没用到

- 第二个专用PLL ( PLLSAI ) 同样用于生成精确时钟,用于SAI1输入时钟,同时还为LCD_TFT接口提供精确时钟,其中,N是用于PLLSAI vco的倍频系数,其取值范围是:192~432;Q是SAI时钟分频系数,其取值范围是:2~15;R是LTDC时钟的分频系数,其取值范围是:2~7;P没用到

- A 看门狗时钟:看门狗时钟源只能是低速的 LSI 时钟

- B RTC时钟源:RTC的时钟源可以选择LSI,LSE,以及HSE分频后的时钟,HSE 分频系数为2~31

- C MCO1 MCO2输出时钟:MCO1是向芯片的PA8引脚输出时钟,它有四个时钟来源分别为:HSI,LSE,HSE,和PLL时钟;MCO2是向芯片的PC9输出时钟,它同样有四个时钟来源分别为:HSE,PLL,SYSCLK以及PLLI2S时钟;MCO输出时钟频率最大不超过100MHz

- D 系统时钟:SYSCLK系统时钟来源有三个方面:HSI,HSE,和PLL,在我们实际应用中,因为对时钟速度要求都比较高我们才会选用STM32F4这种高性能处理器,所以一般情况下,都是采用PLL作为SYSCLK时钟源

- E 以太网PTP时钟 AHB时钟 APB2高速时钟 APB1低速时钟:这些时钟都是来源于 SYSCLK系统时钟,其中以太网PTP时钟是使用系统时钟,AHB,APB2,和APB1时钟是经过SYSCLK时钟分频得来,这里大家记住,AHB最大时钟为168MHz,APB2高速时钟最大频率为84MHz,而APB1低速时钟最大频率为42MHz

- F PLLI2S_R时钟:可以作为I2S时钟源

- G PLLI2S_Q时钟:可以作为SAI1_A和SAI1_B时钟来源

- H PLLSAI_Q时钟:可以作为SAI1_A和SAI1_B时钟来源

- I PLLSAI_R时钟:LCD-TFT ( LTDC ) 接口时钟唯一来源

- J 以太网MAC时钟:对于MII接口来说,必须向外部PHY芯片提供25Mhz的时钟,这个时钟,可以由PHY芯片外接晶振,或者使用STM32F4的MCO输出来提供,然后,PHY芯片再给STM32F4提供ETH_MII_TX_CLK和ETH_MII_RX_CLK时钟,对于RMII接口来说,外部必须提供50Mhz的时钟驱动PHY和STM32F4的 ETH_RMII_REF_CLK,这个50Mhz时钟可以来自PHY,有源晶振,或者STM32F4的MCO

- K USB OTG HS时钟:指外部PHY提供的USB OTG HS ( 60MHZ ) 时钟

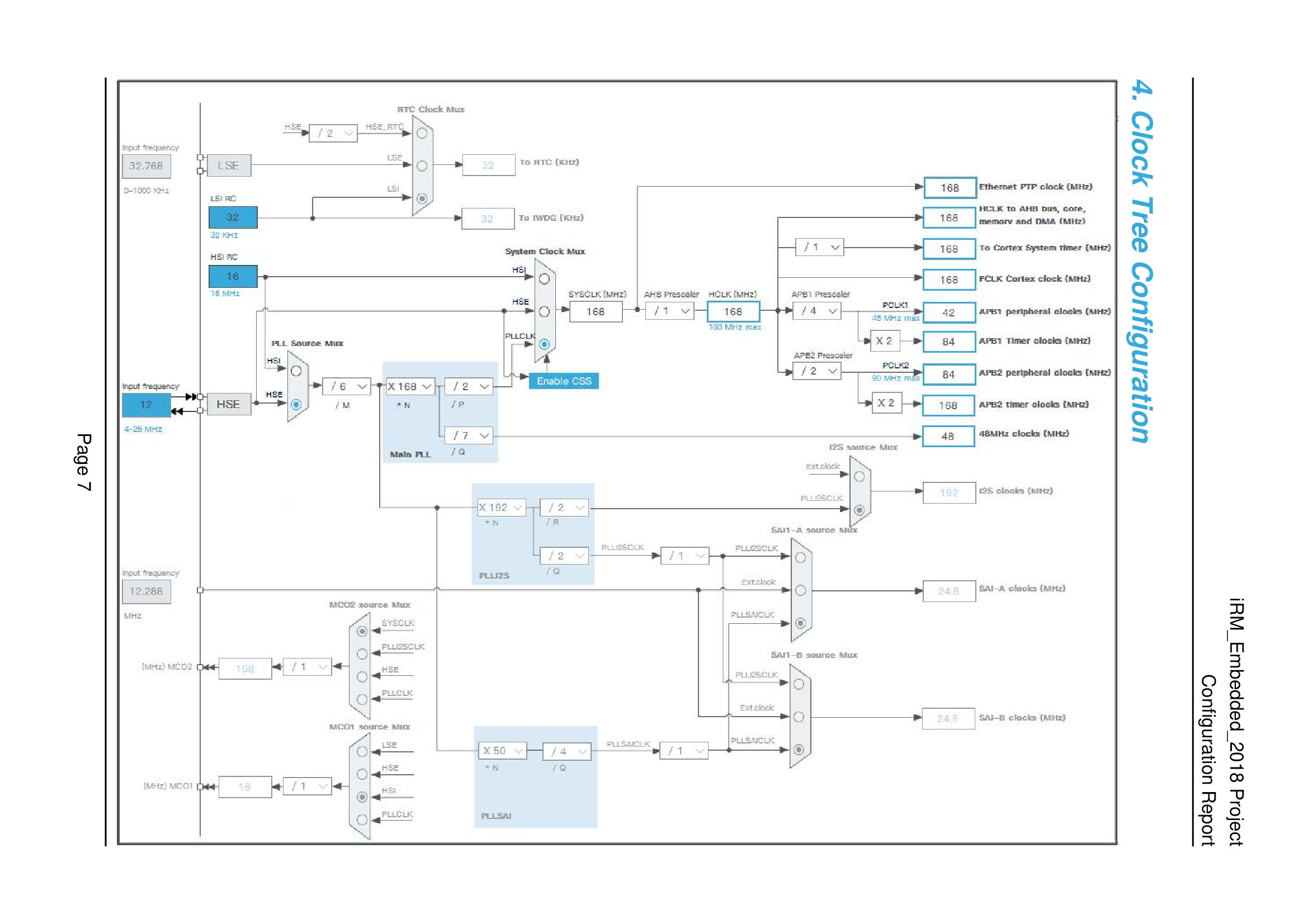

2.0 如何配置Clock Tree?

- 配置方式

- STM32CubeMX静态调控

- 函数动态调控(RM暂时用不上,这部分不讲解)

- STM32CubeMX

- Input frequency改为12MHz

- PLL Source Mux选择HSE,因为HSE比HSI的精确性和最大频率高得多

- System Clock Mux选择PLLCLK,因为即便选择HSE,频率依然不足,而PLLCLK可以成倍增加频率

- 最后,在Ethernet PTP clock那里,输入168MHz,回车,STM32CubeMX会自动配置剩下的东西,到这一步,iRM2018的Clock Tree就已经配置完成了!

- 可能到这一步,I2S source Mux不是48MHz,并且是灰色,无法修改,那就暂时不用动了

如果你成功了,将会看到下面这个配置

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!